Views: 1516

Аналого-цифровой преобразователь с вычислительным модулем.

ВВЕДЕНИЕ

Аналого-цифровой преобразователь (ADC) с вычислительным модулем (ADC2) в 8-разрядном микроконтроллере Microchip имеет встроенные вычислительные функции, которые обеспечивают функции пост-обработки, такие как передискретизация, усреднение и низкочастотная фильтрация.

В этом техническом обзоре дается обсуждение функций ADC2, методов настройки и режимов работы.

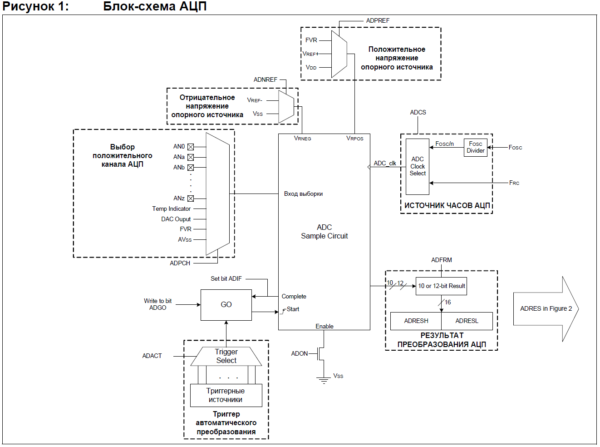

БЛОК-СХЕМА МОДУЛЯ ADC2

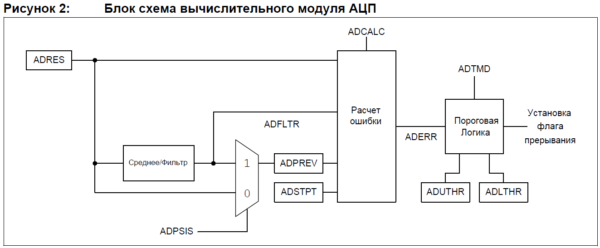

На блок-схеме, показанной на рисунке 1, показан процесс преобразования аналоговых входных сигналов в цифровую форму. Схема разделена на несколько модулей: модуль выбора канала положительного сигнала, модуль выбора источника положительного и отрицательного опорного напряжения, модуля выбора источника тактовой частоты для преобразователя, модуль результата преобразования и модуль выбора источника запуска автоматического преобразования. Модуль выбора входного аналогового канала мультиплексируются в единую схему выборки и удержания аналогового сигнала. Выход модуля (схемы) выборки и удержания подключается к преобразователю, который генерирует двоичное представление аналогового сигнала. Когда АЦП работает с вычислительными функциями, результат преобразования будет передан на блок-схему вычислительной функциональности (см. Рис. 2) для последующей обработки. Результат последующей обработки затем оценивается с использованием расчета ошибок и сравнения пороговых значений.

Описание основных регистров АЦП

Условные обозначения:

R = бит считывания

W = записываемый бит

U = бит не используется, считывается как ‘0’

u = бит неизменяемый

x = бит начальное состояние неизвестно

-n/n = значение в POR и BOR/значение во всех остальных сбросах

‘1’ = бит установлен

‘0’ = бит очищен

Регистры настройки повторений цикла измерений.

ADRPT: регистр настройки цикла повторений измерений

| R/W-0/0 | R/W-0/0 | R/W-0/0 | R/W-0/0 | R/W-0/0 | R/W-0/0 | R/W-0/0 | R/W-0/0 |

| ADRPT<7:0> | |||||||

| bit 7 | bit 6 | bit 5 | bit 4 | bit 3 | bit 2 | bit 1 | bit 0 |

Этот регистр используется в режимах с фильтром нижних частот, вычисление пакетного среднего и вычисление среднего. Число записанное в этот регистр определяет количество измерений которую должен выполнить АЦП для начала обработки данных пороговой логикой. Этот регистр работаем в паре с регистром счетчиком ADCNT.

ADCNT: регистр счетчика повторений измерений

| R/W-x/u | R/W-x/u | R/W-x/u | R/W-x/u | R/W-x/u | R/W-x/u | R/W-x/u | R/W-x/u |

| ADCNT<7:0> | |||||||

| bit 7 | bit 6 | bit 5 | bit 4 | bit 3 | bit 2 | bit 1 | bit 0 |

Этот регистр используется в режимах с фильтром нижних частот, вычисление пакетного среднего и вычисление среднего. В этом регистре содержится текущее число измерений выполненных АЦП.

Выходные регистры фильтра низких частот вычислительного модуля.

В режимах Накопления, вычисление среднего или пакетного среднего (Accumulate, Average и Burst Average) содержащееся в них значение равно ADACC, смещенному по битам ADCRS заданных в регистре ADCON2. В режиме Фильтра низких частот (LPF) это выходной сигнал фильтра нижних частот.

ADFLTRH: регистр старшего байта фильтра АЦП

| R-x | R-x | R-x | R-x | R-x | R-x | R-x | R-x |

| ADFLTR<15:8> | |||||||

| bit 7 | bit 6 | bit 5 | bit 4 | bit 3 | bit 2 | bit 1 | bit 0 |

ADFLTRL: регистр младшего байта фильтра АЦП

| R-x | R-x | R-x | R-x | R-x | R-x | R-x | R-x |

| ADFLTR<7:0> | |||||||

| bit 7 | bit 6 | bit 5 | bit 4 | bit 3 | bit 2 | bit 1 | bit 0 |

Регистр результата текущего измерения АЦП

Для ADFM = 0 – выравнивание результат влево

ADRESH: регистр старшего байта, ADFM = 0

| R/W-x/u | R/W-x/u | R/W-x/u | R/W-x/u | R/W-x/u | R/W-x/u | R/W-x/u | R/W-x/u |

| ADRESH<9:2> | |||||||

| bit 7 | bit 6 | bit 5 | bit 4 | bit 3 | bit 2 | bit 1 | bit 0 |

ADRESL: регистр младшего байта, ADFM = 0

| R/W-x/u | R/W-x/u | U-0 | U-0 | U-0 | U-0 | U-0 | U-0 |

| ADRESL<1:0> | |||||||

| bit 7 | bit 6 | bit 5 | bit 4 | bit 3 | bit 2 | bit 1 | bit 0 |

Для ADFM = 1 – выравнивание результат вправо

ADRESH: регистр старшего байта, ADFM = 1

| R-x | R-x | R-x | R-x | R-x | R-x | R/W-x/u | R/W-x/u |

| ADRESH<9:8> | |||||||

| bit 7 | bit 6 | bit 5 | bit 4 | bit 3 | bit 2 | bit 1 | bit 0 |

ADRESL: регистр младшего байта, ADFM = 1

| R/W-x/u | R/W-x/u | R/W-x/u | R/W-x/u | R/W-x/u | R/W-x/u | R/W-x/u | R/W-x/u |

| ADRESL<7:0> | |||||||

| bit 7 | bit 6 | bit 5 | bit 4 | bit 3 | bit 2 | bit 1 | bit 0 |

Регистр хранения результат предыдущего измерения АЦП

ADPREVH: регистр старшего байта.

| R-x | R-x | R-x | R-x | R-x | R-x | R-x | R-x |

| ADPREVH<15:8> | |||||||

| bit 7 | bit 6 | bit 5 | bit 4 | bit 3 | bit 2 | bit 1 | bit 0 |

ADPREVL: регистр младшего байта.

| R-x | R-x | R-x | R-x | R-x | R-x | R-x | R-x |

| ADPREVL<7:0> | |||||||

| bit 7 | bit 6 | bit 5 | bit 4 | bit 3 | bit 2 | bit 1 | bit 0 |

Содержаться предыдущие значение результата конвертирования АЦП

Если бит ADPSIS = 1:

В этом регистре храниться значение регистра ADFLTR в начале текущего преобразования АЦП.

Если бит ADPSIS = 0:

В этом регистре храниться значение регистра ADRES в начале текущего преобразования АЦП.

Примечание: Если ADPSIS = 0, ADPREVH и ADPREVL форматируются так же, как и ADRES, в зависимости от бит аADFM.

Регистр аккумулятора (накопительный регистр) АЦП

ADACCH: регистр старшего байта.

| R/W-x/u | R/W-x/u | R/W-x/u | R/W-x/u | R/W-x/u | R/W-x/u | R/W-x/u | R/W-x/u |

| ADPREVH<15:8> | |||||||

| bit 7 | bit 6 | bit 5 | bit 4 | bit 3 | bit 2 | bit 1 | bit 0 |

ADACCL: регистр младшего байта.

| R/W-x/u | R/W-x/u | R/W-x/u | R/W-x/u | R/W-x/u | R/W-x/u | R/W-x/u | R/W-x/u |

| ADPREVL<7:0> | |||||||

| bit 7 | bit 6 | bit 5 | bit 4 | bit 3 | bit 2 | bit 1 | bit 0 |

В этом регистре выполняются суммирование результатов вычислений АЦП.

Регистр задание порога вычисления для модуля пороговой логики

ADSTPTH: регистр старшего байта.

| R/W-x/u | R/W-x/u | R/W-x/u | R/W-x/u | R/W-x/u | R/W-x/u | R/W-x/u | R/W-x/u |

| ADSTPTH<15:8> | |||||||

| bit 7 | bit 6 | bit 5 | bit 4 | bit 3 | bit 2 | bit 1 | bit 0 |

ADSTPTL: регистр младшего байта.

| R/W-x/u | R/W-x/u | R/W-x/u | R/W-x/u | R/W-x/u | R/W-x/u | R/W-x/u | R/W-x/u |

| ADSTPTL<7:0> | |||||||

| bit 7 | bit 6 | bit 5 | bit 4 | bit 3 | bit 2 | bit 1 | bit 0 |

В зависимости от режима работы заданного байтами ADCALC, может использоваться для определения ADERR.

Регистры ошибки

ADERRH: регистр старшего байта.

| R-x | R-x | R-x | R-x | R-x | R-x | R-x | R-x |

| ADERRH<15:8> | |||||||

| bit 7 | bit 6 | bit 5 | bit 4 | bit 3 | bit 2 | bit 1 | bit 0 |

ADERRL: регистр младшего байта.

| R-x | R-x | R-x | R-x | R-x | R-x | R-x | R-x |

| ADERRL<7:0> | |||||||

| bit 7 | bit 6 | bit 5 | bit 4 | bit 3 | bit 2 | bit 1 | bit 0 |

Ошибка ADC, от режима работы заданного байтами ADCALC регистра ADCON3.

Регистр задание порога вычисления для модуля пороговой логики, нижнее значение

ADLTHH: регистр старшего байта.

| R/W-x/u | R/W-x/u | R/W-x/u | R/W-x/u | R/W-x/u | R/W-x/u | R/W-x/u | R/W-x/u |

| ADLTHH<15:8> | |||||||

| bit 7 | bit 6 | bit 5 | bit 4 | bit 3 | bit 2 | bit 1 | bit 0 |

ADLTHL: регистр младшего байта.

| R/W-x/u | R/W-x/u | R/W-x/u | R/W-x/u | R/W-x/u | R/W-x/u | R/W-x/u | R/W-x/u |

| ADLTHL<7:0> | |||||||

| bit 7 | bit 6 | bit 5 | bit 4 | bit 3 | bit 2 | bit 1 | bit 0 |

Регистр задание порога вычисления для модуля пороговой логики, вернее значение

ADUTHH: регистр старшего байта.

| R/W-x/u | R/W-x/u | R/W-x/u | R/W-x/u | R/W-x/u | R/W-x/u | R/W-x/u | R/W-x/u |

| ADUTHH<15:8> | |||||||

| bit 7 | bit 6 | bit 5 | bit 4 | bit 3 | bit 2 | bit 1 | bit 0 |

ADUTHL: регистр младшего байта.

| R/W-x/u | R/W-x/u | R/W-x/u | R/W-x/u | R/W-x/u | R/W-x/u | R/W-x/u | R/W-x/u |

| ADUTHL<7:0> | |||||||

| bit 7 | bit 6 | bit 5 | bit 4 | bit 3 | bit 2 | bit 1 | bit 0 |

Регистры ADLTH и ADUTH сравниваются с регистром ADERR для установки битов ADUTHR и ADLTHR в регистре ADSTAT. В зависимости от настройки битов ADTMD в регистре ADCON3 может быть вызвано прерывание результатами этого сравнения.

Регистр настройки режима автоматического запуска измерений АЦП.

ADACT:

| U-0 | U-0 | U-0 | R/W-0/0 | R/W-0/0 | R/W-0/0 | R/W-0/0 | R/W-0/0 |

| – | – | – | ADACT<4:0> | ||||

| bit 7 | bit 6 | bit 5 | bit 4 | bit 3 | bit 2 | bit 1 | bit 0 |

- bit 7-5 Unimplemented: Читаются как ‘0’

- bit 4-0 ADACT<4:0>: Биты выбора автоматического преобразования

11111 = Программное обеспечение выполняет запись в регистр ADPCH

11110 = Зарезервировано, не используйте

11101 = Программное обеспечение выполняет чтение из регистра ADRESH

11100 = Программное обеспечение выполняет чтение из регистра ADERRH

11011 = Зарезервировано, не используйте

*

*

*

10000 = Зарезервировано, не используйте

01111 = Interrupt-on-change Interrupt Flag

01110 = выход компаратора C2

01101 = выход компаратора C1

01100 = выход модуля PWM4

01011 = выход модуля PWM3

01010 = запуск от модуля CCP2

01001 = запуск от модуля CCP1

01000 = выход пост делителя таймера TMR6

00111 = переполнение таймера TMR5_overflow

00110 = выход пост делителя таймера TMR4

00101 = переполнение таймера TMR3_overflow

00100 = выход пост делителя таймера TMR2

00011 = переполнение таймера TMR1_overflow

00010 = переполнение таймера TMR0_overflow

00001 = Pin selected by ADACTPPS

00000 = Авто запуск от внешнего события отключен

ИСТОЧНИК ВЫБОРА КАНАЛА

Регистр выбора входного канала АЦП (ADPCH) определяет, какой канал подключен к схеме выборки и удержания. Выбор источника входного сигнала не ограничивается внешними аналоговыми входами, сигналом может быть и выход периферийного устройства или внутреннего опорного напряжения. Информацию о списке доступных источников см. В техническом паспорте на выбранный микроконтроллер.

Примечание: Одновременно только один канал может быть выбран и преобразован в одном модуле АЦП.

ИСТОЧНИК ОПОРНОГО НАПРЯЖЕНИЯ

Источник опорного напряжения задает диапазон входного напряжения АЦП. Он может быть внешним источником от входов VREF+/-, VDD, FVR или VSS. Положительные и отрицательные опорные напряжения выбирается с помощью битов выбора положительного (ADPREF) и битов выбора отрицательного опорного напряжения (ADNREF) регистра (ADREF) модуля АЦП.

Примечание. Обратитесь к листу данных устройства, поскольку некоторые устройства не имеют битов ADNREF.

Уравнение 1 показывает, как вычислить результат АЦП с помощью VREF+/- контактов. Важно отметить, что VREF+ всегда должен быть больше VREF-, а VREF- должен иметь значение, большее или равное нулю.

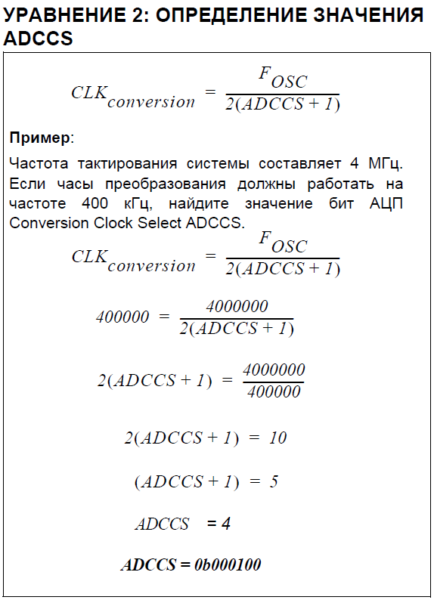

ИСТОЧНИКА ТАКТОВОГО СИГНАЛА ПРЕОБРАЗОВАТЕЛЯ

Преобразователь имеют несколько источников тактового сигнала, от может тактироваться либо от основного генератора, через делитель с кратностью от двух (то есть, 2, 4, 6, … 128), либо от выделенного внутреннего RC-генератора. Выбор источника тактового сигнала управляет бит (ADCS) в регистре управления (ADCON0) и биты выбора делителя частоты (ADCCS) регистра (ADCLK). Когда бит ADCS очищен, АЦП тактируется от FOSC в соответствии со значением делителя ADCCS (см. Уравнение 2).

Желаемого тактовая частота АЦП должен соответствовать характеристикам синхронизации преобразования АЦП, предусмотренные в паспорте выбранного микроконтроллера. Когда бит ADCS установлен, АЦП тактируется от внутреннего RC-генератора FRC.

ТРЕБОВАНИЯ АЦП К ВРЕМЕНИ СБОРА ДАННЫХ

Время сбора данных – это время, необходимое АЦП для захвата входного напряжения во время выборки. Для того, чтобы АЦП соответствовал заданной точности, конденсатор образца и удерживания (CHOLD) должен иметь достаточное время для установления уровня напряжения входного канала до начала фактического преобразования. Если для сбора данных недостаточно времени, преобразование будет неточным. На время сбора данных влияет множество факторов. Это следующие: CHOLD, импеданс промежуточных соединений (RIC), выходной импеданс аналогового источника (RS) и импеданс переключателя (RSS). Максимальный рекомендуемый импеданс для аналоговых источников в 10-битном и 12-битном АЦП составляет 10 кОм и 4,4 кОм соответственно. См. Спецификацию конкретного устройства в отношении уравнения, которое вычисляет минимальное время сбора данных для конкретного приложения.

ИСТОЧНИК ТРИГГЕРА АВТОМАТИЧЕСКОГО ПРЕОБРАЗОВАНИЯ

Триггер автоматического преобразования позволяет системе планировать последовательности сбора и преобразования без вмешательства программного обеспечения. Когда возникает нарастающий фронт выбранного источника, бит ADGO устанавливается. Источники для триггера автоматического преобразования можно найти в листе данных устройства. В приложении эти источники, запуска автоматического преобразования, можно использовать для установки периода выборки АЦП. Источник автоматического преобразования выбирается с использованием регистра управления, триггером автоматического преобразования АЦП, (ADACT).

НЕПРЕРЫВНЫЙ РЕЖИМ RETRIGGER

RETRIGGER непрерывного режима можно включить, установив бит разрешения непрерывной работы A/D (ADCONT) регистра ADCON0 в «1» (ADCONT = 1). Включение непрерывного режима, позволяет начать автоматическое повторение выборки после проверки порога. В этом режиме бит состояния преобразования (ADGO) регистра ADCON0 остается установленным до тех пор, пока не будут выполнены пороговые условия в соответствии с выбранным в ADTMD и битом прерывания прерывания A/D (ADSOI) регистра ADCON3.

SLEEP MODE (РЕЖИМ СНА)

Работа модуля АЦП2 в спящем режиме требуется использовать специальный источник тактового сигнала – RC-генератор (FRC). Когда преобразование будет завершено, устройство проснется, если прерывание АЦП включено. Если прерывание АЦП отключено, устройство останется в режиме сна.

Во время сна, когда источник синхронизации настроен на FRC, при получении активации с внешнего триггера АЦП выполнит преобразование и установит бит флага прерывания (ADIF). Если во время сна при получении активации с внешнего триггера, когда источник синхронизации установлен на что-то иное, кроме FRC, триггер запоминается, но преобразование не начинается, пока устройство не выйдет из режима сна.

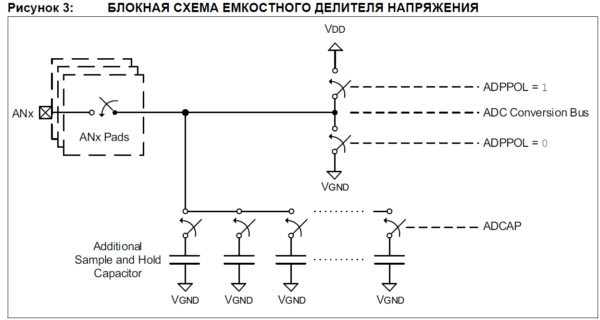

ОСОБЕННОСТИ ЕМКОСТНОГО ДЕЛИТЕЛЯ НАПРЯЖЕНИЯ (CVD)

Одной из особенностей модуля ADCC является CVD. CVD использует конденсаторы в качестве компонентов для цепи делителя напряжения. На рисунке 3 показана блок-схема аппаратной части CVD модуля ADCC. Эта функция ADCC позволяет пользователю выполнять относительное измерение емкости на любом канале АЦП с использованием внутреннего АЦП CHOLD в качестве эталона.

CHOLD и внешний емкостной датчик, подключенный к выбранному аналоговому каналу, предварительно заряжаются до VDD или VSS в зависимости от выбранного бита полярности предварительной зарядки (ADDPOL) регистра ADCON1, а цепь между CHOLD и внешним емкостным датчиком отключен. Время, в течение которого происходит эта зарядка, зависит от значения, установленного в регистре ADPRE. Эта предварительная зарядка активируется путем записи ненулевого значения в регистр ADPRE. Если ADPRE установлен на «0», когда начинается преобразование АЦП, этап предварительной зарядки пропускается.

Этап сбора представляет собой измеренное время для напряжения CHOLD для зарядки или разряда с выбранного аналогового канала. Во время сбора данных между предварительно заряженным CHOLD и выбранным аналоговым каналом образуется емкостной делитель напряжения, в то время как выбранный аналоговый канал подключен к CHOLD. В результате, заряд между CHOLD и внешним емкостным датчиком, подключенным к выбранному аналоговому каналу, теперь распределен равномерно. После того, как перенос заряда стабилизирован, напряжение CHOLD измеряется ADCC и используется для определения емкости емкости внешней емкости.

Еще одна уникальная особенность оборудования CVD – дополнительная дополнительная емкость, которую можно добавить параллельно с CHOLD. Эта дополнительная емкость может быть выбрана через регистр выбора дополнительного конденсатора ADC (ADCAP). Он используется в приложениях CVD, улучшая соответствие между внутренней и внешней емкостью для лучшей чувствительности.

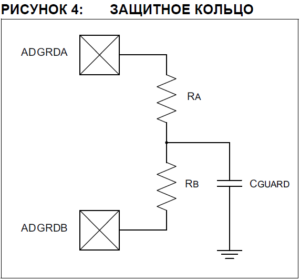

ЗАЩИТНОЕ КОЛЬЦО ЦЕПИ УПРАВЛЕНИЯ

Модуль ADCC также оснащен защитным кольцом (см. Рис. 4), который поддерживает аппаратное CVD. Два цифровых выхода и соответствующие резисторы делителя напряжения, используются для управления напряжением защитного кольца. Цепь защитного кольца, используется для генерации сигнала в фазе с сигналом чувствительности CVD для минимизации влияния паразитной емкости на чувствительные электроды. Он также может использоваться в качестве взаимного привода для взаимного емкостного зондирования. Для получения дополнительной информации об активном защите и взаимном приводе см. Примечание к применению AN1478 «Методы mTouch ™ Sensing Solution для емкостного делителя напряжения» (DS01478).

ADCC обеспечивает два выхода защитного кольца, контакты ADGRDA и ADGRDB. Для устройства, имеющего выбор периферийных выводов (PPS), ADGRDA и ADGRDB могут быть переназначены на любые выходные выводы, используя регистр выбора выхода PPS (RxyPPS).

«Rxy» в RxyPPS является держателем места для идентификатора штыря (например, RB0PPS = 0x24 и RB1PPS = 0x25), где RB0 сконфигурирован как выходной вывод ADGRDA и RB1 в качестве выходного вывода ADGRDB. Обратите внимание, что значения селектора для PPS ADGRDA и ADGRDB зависят от устройства.

Таблица 1: Режим вычисления ошибки, от режима выбранной работы.

| ADCALC | Расчет ошибки |

Режим работы | |

| ADDSEN = 0 Режим одиночной выборки |

ADDSEN=1 CVD Режим двойной выборки(1) |

||

| 000 | ADRES-ADPREV | ADRES-ADPREV | Первая производная единичного измерения(2) First derivative of single measurement |

| Фактический CVD результат в CVD(2) Actual CVD result in CVD |

|||

| 001 | ADRES-ADSTPT | (ADRES-ADPREV)-ADFLTR | Фактический результат по сравнению с заданным значением Actual result vs. setpoint |

| 010 | ADRES-ADFLTR | (ADRES-ADPREV)-ADFLTR | Фактический результат по сравнению с усредненным/отфильтрованным значением Actual result vs. averaged/filtered value |

| 011 | Зарезервировано | ||

| 100 | ADPREV-ADFLTR | ADPREV-ADFLTR | Первая производная отфильтрованного значения (3) отрицательная First derivative of filtered value negative |

| 101 | ADFLTR-ADSTPT | ADFLTR-ADSTPT | Среднее/отфильтрованное значение по сравнению с заданным значением Average/filtered value vs. setpoint |

| 110 | Зарезервировано | ||

| 111 | Зарезервировано | ||

Примечание:

- Когда ADPSIS = 0, значение из (ADRES-ADPREV) равно (S2-S1).

- Когда ADPSIS = 0.

- Когда ADPSIS = 1.

Вычисленный результат сохраняется в ADERR, который можно сравнить с выбранным верхним или нижним порогом. Эти два пороговых значения могут быть установлены путем изменения регистров верхнего уровня ADC (ADUTH) и регистров нижнего порога ADC (ADLTH). Результат true, основанный на сравнении, показанном в таблице 2, вызовет прерывание. Этот пороговый тест выбирается через биты выбора режима порогового прерывания (ADTMD) регистра ADCON3.

Таблица 2: Режим прерывания от условия порога.

| ADTMD | Условие прерывания | Выходы компаратора | ||

| ADERR<ADLTH | ADERR>ADUTH | |||

| 000 | Нет прерываний | |||

| 001 | Ошибка < Нижний порог | True | ||

| 010 | Ошибка ≥ Нижний порог | False | ||

| 011 | Ошибка между порогами | False | AND | False |

| 100 | Ошибка вне пороговых значений | True | OR | True |

| 101 | Ошибка ≤ Верхний порог | False | ||

| 110 | Ошибка > Верхний порог | True | ||

| 111 | Прерывание для всех данных | |||

Режимы вычислений

Задаются битами ADMD<2:0>: в регистре ADCON2:

- ADMD<2:0> Режимы работы

111-101 = Зарезервировано

100 = Low-pass Filter mode (режим фильтра нижних частот)

011 = Burst Average mode (режим вычисления среднего из пакетного измерения)

010 = Average mode (режим вычисления среднего)

001 = Accumulate mode (режим накопления)

000 = Basic (Legacy) mode (Основной (устаревший) режим)

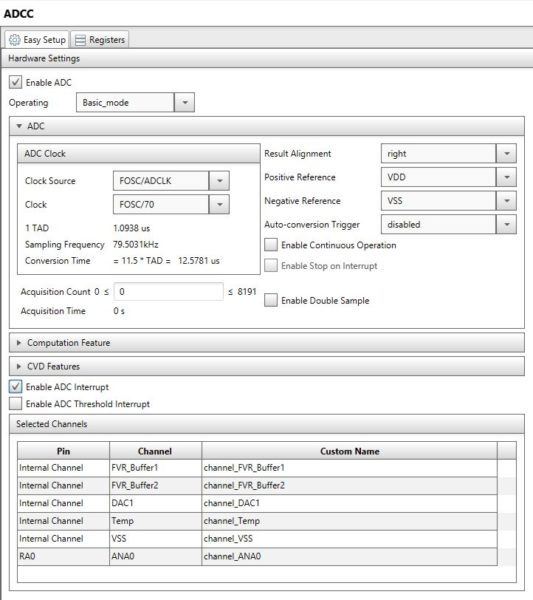

Базовый режим

Основной режим работы АЦП2 имитирует работу устаревших АЦП. В этом режиме логика аккумулятора не активна. Это означает, что значения регистров A/D Accumulator (ADACC) и A/D Repeat Count (ADCNT) не используются на протяжении всей операции, и регистр ADRES используется во всех режимах. Базовый режим АЦП2 выбирается путем установки битов выбора режима работы (ADMD) регистра управления 2 (ADCON2) на 0 (ADMD = 000). При использовании функции автоматического запуска модуля выборка ввода может быть легко вызвана другими периферийными устройствами и внешними источниками. Результат преобразования можно сравнить с пороговой уставкой, которая может инициировать бит флага прерывания аналого-цифрового преобразователя (ADTIF) регистра PIR1.

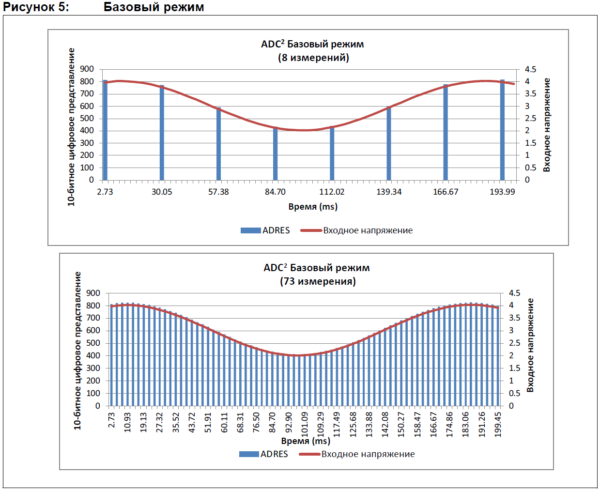

На рисунке 5 показан результат преобразования ADC в базовом режиме с использованием разных частот дискретизации.

Пример обработки данных измерения (с использованием MCC)

В функцию прерывания ADCC_ISR(), добавить выражение rezizm= ADCC_GetConversionResult();

void ADCC_ISR(void)

{

// загрузить данные измерения

rezizm = ADCC_GetConversionResult();

// Clear the ADCC interrupt flag

PIR1bits.ADIF = 0;

LED8=!LED8;

if (ADCC_ADI_InterruptHandler)

ADCC_ADI_InterruptHandler();

}

В переменной rezizm будем получать данные измерения.

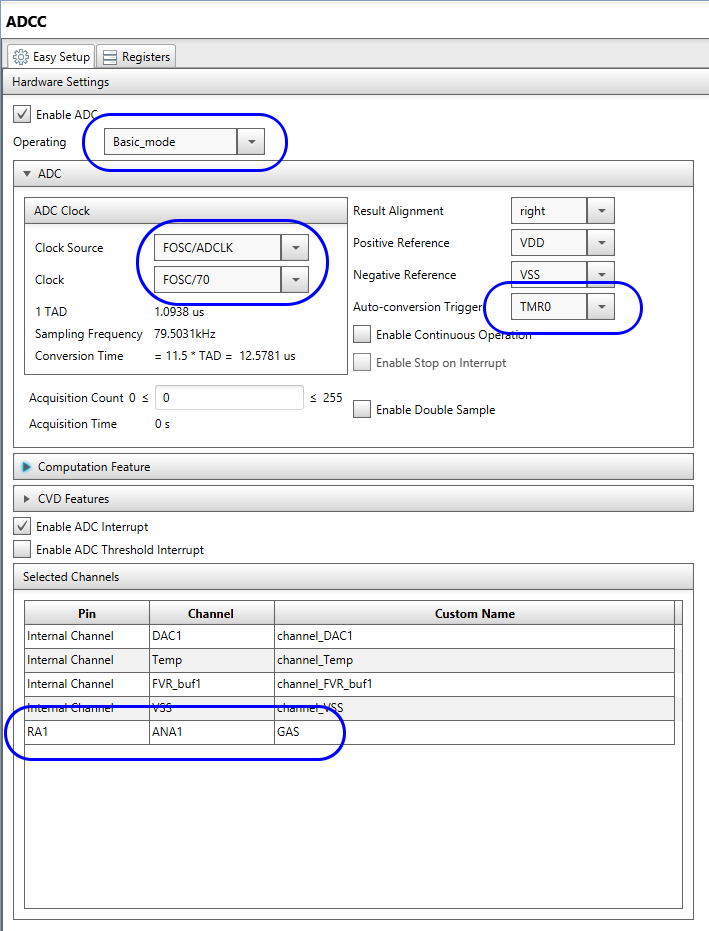

Дополнение. Настройка базового режима, с автоматическим запуском от таймера Т0, вход AN1

Кофигурирование в МСС

Создадим фунцию которую подключем в прерывания АЦП, для получение данных преобразования.

void ACP_USE(void)

{

accumulatorValue = ADCC_GetConversionResult();

}

В процессе инициализации микроконтроллера выполним следующее:

//--------------------------------------------------------------------------

ADCC_StartConversion(GAS); // выбор канала преобразования

ADCC_SetADIInterruptHandler(&ACP_USE); // настройка обработки значения от АЦП

//--------------------------------------------------------------------------

Выбор входа АЦП с которого будут преобразовываться данные и через функцию ADCC_SetADIInterruptHandler внедрем наш код ACP_USE который будет выполняться в цикле прерывания. Переменная accumulatorValue должна быть описанная как внешняя и при чтении её мы влюбое время получим “сырые данные АЦП”.

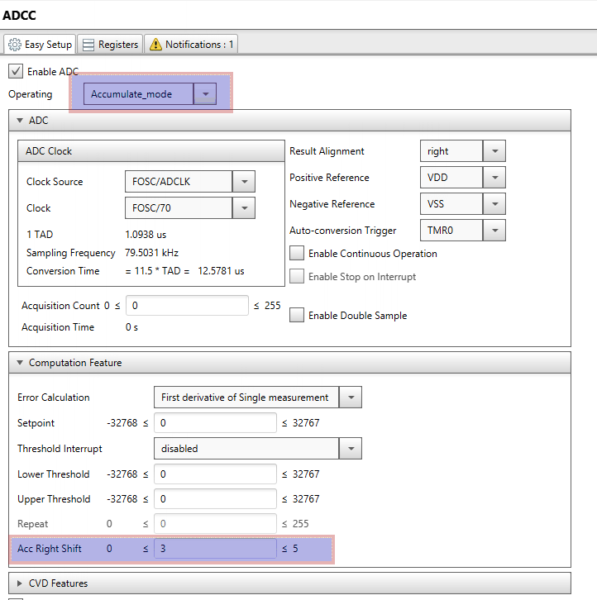

Режим накопления

Режим Накопления для ADC2 выбирается путем установки битов ADMD регистра ADCON2 в 1 (ADMD = 001). В этом режиме цифровое представление аналогового входного сигнала в 10-битном или 12-битном регистре ADRES накапливается в 16-битном или 18-битном регистре ADACC соответственно. С каждым образцом ADCNT увеличивается, указывая количество накопленных проб. Значение ADCNT насыщается на 255 образцах и не сбрасывается в ноль. Поскольку значение, накапливаемое в ADACC, является 10-битным или 12-разрядным значением ADRES, ADACC может переполняться после всего лишь 64 выборок. Это событие вызовет бит переполнения АЦП (ADAOV) регистра состояния ADSTAT.

Накопленное значение может быть сдвинуто вправо до шести раз, изменив значение выбора вычисления сдвига в право накопленного значение битов (ADCRS) регистра ADCON2. Это означает, что накопленное значение эффективно делится на два (2ADCRS). Результат сдвинутого накопленного значения сохраняется в регистре ADFLTR. Таблица 3 показывает пример данных режима Аккумулятора с 10-разрядным регистром ADRES.

Таблица 3: ПРИМЕР РЕЖИМА НАКОПЛЕНИЯ.

| ADCNT

счетчик выполненных измерений АЦП |

ADCRS

заданный сдвиг результата измерения (вправо) |

VINPUT

входное напряжение |

10-bit ADRES

значение в регистре |

16-bit ADACC

значение в регистре |

16 bit ADFLTR

значение в регистре от выполнения операции сдвига в право числа хранящегося в регистре ADACC |

| 1 | 3 | 2.5V | 514 | 514 | 64 |

| 2 | 3 | 2.5V | 514 | 1028 | 128 |

| 3 | 3 | 2.5V | 514 | 1542 | 192 |

| 4 | 3 | 2.5V | 514 | 2056 | 257 |

| 5 | 3 | 2.5V | 514 | 2570 | 321 |

| 6 | 3 | 2.5V | 514 | 3084 | 385 |

| 7 | 3 | 2.5V | 514 | 3598 | 449 |

| 8 | 3 | 2.5V | 514 | 4112 | 514 |

Пример обработки данных измерения (с использованием MCC)

Режим накопление измеренных данных с вычислением среднего программным обеспечением

void ADCC_ISR(void)

{

// загрузить данные измерения

if(ADCNT>=20) // задаем количество накоплений до момента вычисления

{

rezizm = ADCC_GetAccumulatorValue()/ADCNT; // вычисление среднего

ADCNT=0; // сброс счетчика измерение

ADCC_ClearAccumulator(); // сброс аккумулятора

}

// Clear the ADCC interrupt flag

PIR1bits.ADIF = 0;

LED8=!LED8;

if (ADCC_ADI_InterruptHandler)

ADCC_ADI_InterruptHandler();

}

Если задать сдвиг равный 3, это деление значения аккумулятора на 8 и читать данные из регистра ADFLTR, при этом цикл измерения сделать равным 8

void ADCC_ISR(void)

{

// загрузить данные измерения

if(ADCNT>=8) // задаем количество накоплений до момента вычисления

{

rezizm = ADCC_GetFilterValue(); // вычисление среднего

ADCNT=0; // сброс счетчика измерение

ADCC_ClearAccumulator(); // сброс аккумулятора

}

// Clear the ADCC interrupt flag

PIR1bits.ADIF = 0;

LED8=!LED8;

if (ADCC_ADI_InterruptHandler)

ADCC_ADI_InterruptHandler();

}

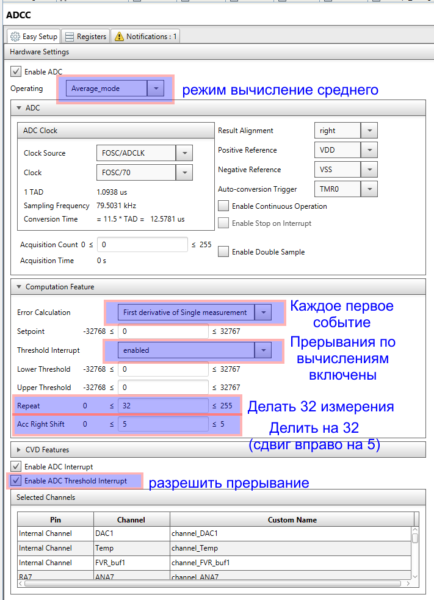

Режим вычисления среднего

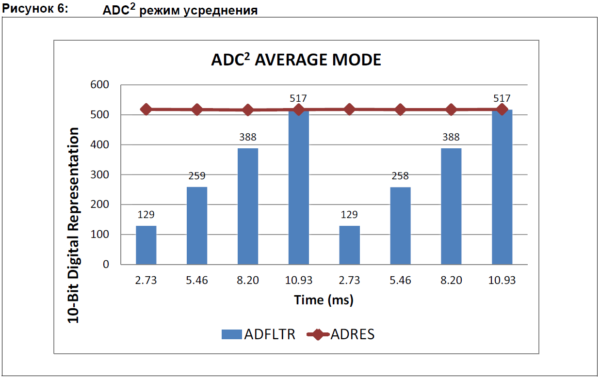

Режим вычисления среднего АЦП2 выбирается путем установки битов ADMD регистра ADCON2 в 2 (ADMD = 010). Этот режим похож на режим Накопления, в котором ADACC накапливает образцы данных и приращения ADCNT с каждым образцом, за исключением того, что количество сэмплов, накапливаемых в этом режиме, соответствует значению, установленному в регистре настройки повторения A/D (ADRPT). Когда ADCNT равно ADRPT, значение, хранящееся в регистре фильтра ADC (ADFLTR), становится средним значением входного сигнала. Фактически, значение, сохраненное в ADFLTR, является результирующим фактором ADACC и ADRPT. Среднее значение входного напряжения может быть правильно рассчитано, когда ADRPT равно Уравнению 3. Когда ADCNT превышает значение ADRPT, регистры ADCNT и ADACC сбрасываются автоматически, чтобы снова накапливать образцы данных. В таблице 4 показаны образцы данных для режима усреднения, где ADCRS равно двум, а ADRPT равно четырем. Это означает, что для получения среднего значения будут накапливаться четыре отсчета, а затем по пятому образцу аккумулятор автоматически очищается, как показано на рисунке 6.

Уравнение 3: Вычисление значения для регистра ADRPT

ADRPT = ADACC >> 2ADCRS

Таблица 4: Пример режима усреднения.

| ADCRS

заданный сдвиг результата измерения (вправо) |

ADRPT

заданное значение для вычисления среднего 4 измерения |

SAMPLE | ADCNT

счетчик выполненных измерений АЦП |

10-bit ADRES результат измерения |

ADACC ADACC = ADACC + ADRES |

ADFLTR

ADFLTR = ADACC >> 2ADCRS |

| 2 | 4 | 0 | 1 | 518 | 518 | 129 |

| 2 | 4 | 1 | 2 | 518 | 1036 | 259 |

| 2 | 4 | 2 | 3 | 516 | 1552 | 388 |

| 2 | 4 | 3 | 4 | 517 | 2069 | 517 |

| 2 | 4 | 4 | 1 | 517 | 518 | 129 |

| 2 | 4 | 5 | 2 | 517 | 1035 | 258 |

| 2 | 4 | 6 | 3 | 5174 | 1552 | 388 |

| 2 | 4 | 7 | 4 | 518 | 2070 | 517 |

| 2 | 4 | 8 | 1 | 517 | 517 | 129 |

| 2 | 4 | 9 | 2 | 516 | 1033 | 258 |

Пример, 32 измерений вычисление среднего значения.

Пример, 32 измерений вычисление среднего значения.

Настройка АЦП (автозапуск от таймера TMP0), используем прерывания от модуля вычислений.

В прерывание ADCC_ThresholdISR добавим чтение регистров фильтра ADFLTR.

void ADCC_ThresholdISR(void)

{

// Clear the ADCC Threshold interrupt flag

rezizm = ADCC_GetFilterValue(); // получение среднего значения от 32 измерений

PIR1bits.ADTIF = 0;

LED8=!LED8; // для теста работы прерывания

if (ADCC_ADTI_InterruptHandler)

ADCC_ADTI_InterruptHandler();

}

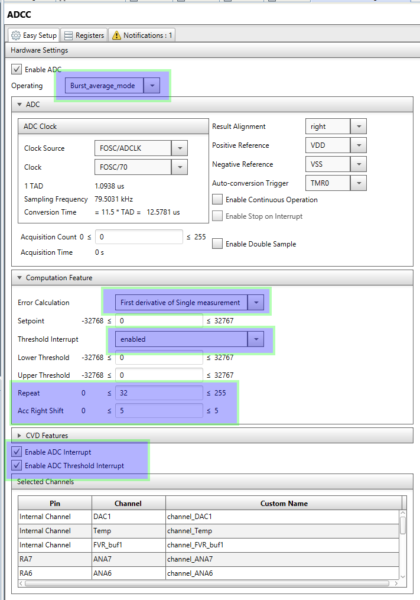

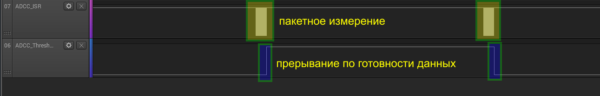

Режим взрывного (пакетного) среднего

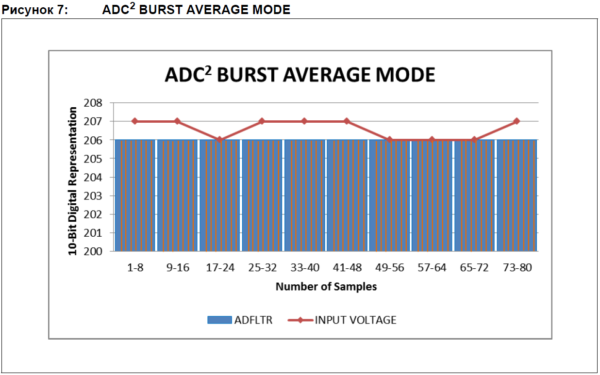

Как и режим усреднения, режим (Burst Average) взрывного среднего усредняет входной сигнал, за исключением того, что выборка выполняется быстро после одного триггера (см. Рис. 7). Это означает, что в одном преобразовании все образцы данных накапливаются до установленного ADRPT, и когда ADCNT соответствует установленному значению ADPRT, достигается среднее значение входного сигнала. Как только среднее значение пакета достигнет, может быть выполнено сравнение порогового значения. Для получения дополнительной информации см. Раздел «Пороговое сравнение». Section “Threshold Comparison”. Следовательно, ADTIF может появляться только в конце выборки полного пакета. Режим взрывного среднего выбирается путем установки битов ADMD в регистре ADCON2 в 3 (ADMD = 011). Таблица 5 показывает выборку данных для режима пакетного среднего.

Таблица 5: Пример работы режима взрывного (пакетного) среднего.

| SAMPLE | TRIGGER | ADCNT | ADCRS | ADRPT | 10-bit ADRES | ADACC | ADFLTR |

| 1-8 | 1 | 8 | 3 | 8 | 207 | 1655 | 206 |

| 9-16 | 2 | 8 | 3 | 8 | 207 | 1653 | 206 |

| 17-24 | 3 | 8 | 3 | 8 | 206 | 1653 | 206 |

| 25-32 | 4 | 8 | 3 | 8 | 207 | 1653 | 206 |

| 33-40 | 5 | 8 | 3 | 8 | 207 | 1652 | 206 |

| 41-48 | 6 | 8 | 3 | 8 | 207 | 1653 | 206 |

| 49-56 | 7 | 8 | 3 | 8 | 206 | 1654 | 206 |

| 57-64 | 8 | 8 | 3 | 8 | 206 | 1652 | 206 |

| 65-72 | 9 | 8 | 3 | 8 | 206 | 1655 | 206 |

| 73-80 | 10 | 8 | 3 | 8 | 207 | 1654 | 206 |

Пример настроим на получение данных среднего из 32 измерений.

Пример настроим на получение данных среднего из 32 измерений.

Все настройки как и в предыдущем примере, только режим пакетного среднего. Смысл его прост, при получении запуска от внешнего устройства (триггера) АЦП выполняет заданное количество измерений в регистре ADRPT, потом автоматически вычисляется среднее которое мы можем получить во время прерывания функции ADCC_ThresholdISR.

Например, запуск настроен на 10 мс от таймера TMP0.

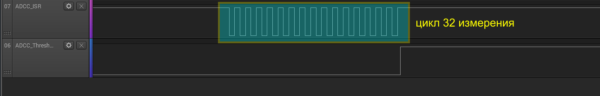

Как выглядит сам процесс измерения, каждый строб это прерывание по окончанию процесса конвертирования АЦП.

Как выглядит сам процесс измерения, каждый строб это прерывание по окончанию процесса конвертирования АЦП.

void ADCC_ThresholdISR(void)

{

// Clear the ADCC Threshold interrupt flag

chanll[Channel_indicator] = ADCC_GetFilterValue(); // вычисление среднего

PIR1bits.ADTIF = 0;

LED8=!LED8; // для теста работы прерывания

if (ADCC_ADTI_InterruptHandler)

ADCC_ADTI_InterruptHandler();

}

Режим фильтра нижних частот

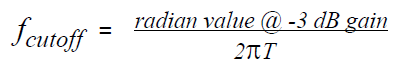

Фильтр нижних частот пропускает сигналы с частотами ниже его обрезания и ослабляет частоты выше его отсечки. Этот режим выбирается путем установки битов ADMD регистра ADCON2 в 4 (ADMD = 100). ADCRS определяет порядок фильтра нижних частот. Учитывая значение радиана в таблице 6, частоту среза (коэффициент усиления @ – 3dB) можно рассчитать, используя уравнение 4.

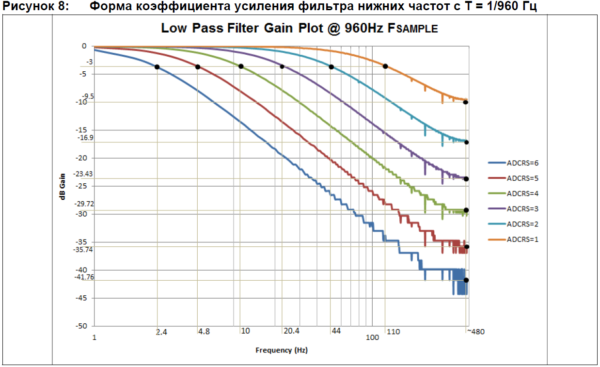

На рисунке 8 показано усиление графика кодирования 10-разрядного низкочастотного фильтра ADCC с использованием интервала T выборки 1/960 Гц. Эта цифра представляет собой фактические 10-битные данные АЦП и демонстрирует выборки и эффект квантования.

Таблица 6: Примеры частоты фильтра.

| ADCRS | Radian Value @ -3 dB Gain (radian) |

Gain @ f=1/2T (dB) |

T (3) (sec) |

Fcutoff (3) (Hz) |

FNyquist = 1/2T(3) (Hz) |

| 1 | 0.72 | -9.5 | 1/960 Hz | 110.01 | 480 |

| 2 | 0.284 | -16.9 | 1/960 Hz | 43.39 | 480 |

| 3 | 0.134 | -23.5 | 1/960 Hz | 20.47 | 480 |

| 4 | 0.065 | -29.8 | 1/960 Hz | 9.93 | 480 |

| 5 | 0.032 | -36 | 1/960 Hz | 4.89 | 480 |

| 6 | 0.016 | -42 | 1/960 Hz | 2.44 | 480 |

Примечание:

- Не все значения поддерживаются на всех устройствах.

- T = интервал выборки (сек).

- Т, Fcutoff и FNyquist являются примерами.

Сводная таблица режимов.

Таблица 7: ADC2 резюме результатов вычисления.

| Режим | ADMD | Обстоятельство очистки бит |

Значение после завершения Trigger | Значение при прерывании ADTIF | |||

| ADACC

и ADCNT |

ADACC | ADCNT | ADAOV | ADFLTR | ADCNT | ||

| Базовый | 0 | ADACLR = 1 | без изменений | без изменений | n/a | n/a | подсчет |

| Накопительный | 1 | ADACLR = 1 | S+ADACC или (S2-S1) + ADACC |

ADCNT+1, но не более 255 |

ADACC переполнение |

ADACC/2ADCRS | подсчет |

| Среднее | 2 | ADACLR = 1

или |

S+ADACC или (S2-S1) + ADACC |

ADCNT+1, но не более 255 |

ADACC переполнение |

ADACC/2ADCRS | подсчет |

| Взрывное (пакетное) среднее |

3 | ADACLR = 1

или |

Каждое повторение: то же, что и Среднее Окончание с сумма всех выборок |

Каждое повторение: то же, что и Среднее Окончание ADCNT = ADRPT |

ADACC переполнение |

ADACC/2ADCRS | ADRPT |

| Фильтр нижних частот |

4 | ADACLR = 1 | S + ADACC – ADACC/2ADCRS или (S2 – S1) + ADACC – ADACC/2ADCRS |

ADCNT+1, но не более 255 |

ADACC переполнение |

Отфильтрованное значение | подсчет |

Естественно все возможности нового модуля АЦП в этой краткой статье разобрать не получиться, но главные возможности с нее вынести надеюсь можно.

Описание в pdf

Analog-to-Digital Converter with Computation Technical Brief - русское описание 1.08 MB 459 downloads

Аналого-цифровой преобразователь (ADC) с вычислительным...Это может быть интересно

Цифровой тахометр для автомобиля CH-С3300Views: 2089 Тахометр Ch-С3300 предназначен для индикации и контроля оборотов, времени работы и максимальных оборотов развиваемых двигателем во время поездки. Датчиком может использоваться как обычный контактный прерыватель или выход датчика …

Цифровой тахометр для автомобиля CH-С3300Views: 2089 Тахометр Ch-С3300 предназначен для индикации и контроля оборотов, времени работы и максимальных оборотов развиваемых двигателем во время поездки. Датчиком может использоваться как обычный контактный прерыватель или выход датчика … Мониторинг температурыViews: 1489 Настоящий проект создан как обучающий с применением библиотек ds18b20 и LCDHD44780 и компилятора Microchip MPLAB XC8 C Compiler V1.12. Если необходимо иметь информацию по состоянию температуры в помещении или в здании, с количеством до 6 точек (16), то …

Мониторинг температурыViews: 1489 Настоящий проект создан как обучающий с применением библиотек ds18b20 и LCDHD44780 и компилятора Microchip MPLAB XC8 C Compiler V1.12. Если необходимо иметь информацию по состоянию температуры в помещении или в здании, с количеством до 6 точек (16), то … MCC PIC24 – модуль REAL-TIME CLOCK AND CALENDAR (RTCC)Views: 700 RTCC предоставляет пользователю часы реального времени и функция календаря (RTCC), точность “хода” может быть откалибрована. Основные особенности модуля RTCC: • Работает в режиме глубокого сна. • Возможность выбора источника …

MCC PIC24 – модуль REAL-TIME CLOCK AND CALENDAR (RTCC)Views: 700 RTCC предоставляет пользователю часы реального времени и функция календаря (RTCC), точность “хода” может быть откалибрована. Основные особенности модуля RTCC: • Работает в режиме глубокого сна. • Возможность выбора источника … Ultrasonic Level Meters – ULM –53LViews: 806 Измерение расстояния при помощи ультра звукового датчика ULM–53L–10. Диапазон измерения от 0,5 м до 10 м, полностью пластмассовый излучатель PVDF, механическое соединение фланцем из полиэтилена HDPE (исполнение “N”) Характеристики …

Ultrasonic Level Meters – ULM –53LViews: 806 Измерение расстояния при помощи ультра звукового датчика ULM–53L–10. Диапазон измерения от 0,5 м до 10 м, полностью пластмассовый излучатель PVDF, механическое соединение фланцем из полиэтилена HDPE (исполнение “N”) Характеристики … PIC18 – модуль DMAViews: 1366 Введение Модуль прямого доступа к памяти (DMA) предназначен для обслуживания передачи данных непосредственно между различными областями памяти без вмешательства процессора. Исключив при этом необходимость в интенсивной обработки …

PIC18 – модуль DMAViews: 1366 Введение Модуль прямого доступа к памяти (DMA) предназначен для обслуживания передачи данных непосредственно между различными областями памяти без вмешательства процессора. Исключив при этом необходимость в интенсивной обработки … Altium Designer first projectViews: 547 Эта статья подразумевает, что у вас установлен и настроен Altium Designer как описано в статье Altium Designer my setup system and project structure. Обратите внимание! Библиотека постоянно обновляется, …

Altium Designer first projectViews: 547 Эта статья подразумевает, что у вас установлен и настроен Altium Designer как описано в статье Altium Designer my setup system and project structure. Обратите внимание! Библиотека постоянно обновляется, … Проект с использованием MCC часть 12-1Views: 1138 В настоящее время без визуализации информации уже не интересно. Поэтому научимся выводить информацию на дисплей. Для это возьмет простенький OLED RET012864E/REX012864J я такой приобретал в фирме “Гамма-Украина”, описание можно …

Проект с использованием MCC часть 12-1Views: 1138 В настоящее время без визуализации информации уже не интересно. Поэтому научимся выводить информацию на дисплей. Для это возьмет простенький OLED RET012864E/REX012864J я такой приобретал в фирме “Гамма-Украина”, описание можно … LCD индикаторы на драйвере ML1001Views: 2063 ML1001 – статический LCD GOG (чип в стекле) драйвер для 40-сегментного LCD в позолоченном противоударном исполнении. На них можно каскадно строить цельные из 80 или 120 сегментов LCD индикаторы. …

LCD индикаторы на драйвере ML1001Views: 2063 ML1001 – статический LCD GOG (чип в стекле) драйвер для 40-сегментного LCD в позолоченном противоударном исполнении. На них можно каскадно строить цельные из 80 или 120 сегментов LCD индикаторы. … Мультимедийная сеть – AVC-LAN TOYOTAViews: 5924 AVC LAN – протокол обмена данными мультимедийных систем автомобиля. Кодирование данных. При кодировании различаться три типа данных : преамбула – её назначение, это сообщение устройствам на шине, что начинается передача данных. …

Мультимедийная сеть – AVC-LAN TOYOTAViews: 5924 AVC LAN – протокол обмена данными мультимедийных систем автомобиля. Кодирование данных. При кодировании различаться три типа данных : преамбула – её назначение, это сообщение устройствам на шине, что начинается передача данных. … Одноканальный емкостной сенсор – AT42QT1012Views: 2496 Описание сенсора [wpdm_file id=242] Незаконченный проект, так-как сенсор не оправдал своего назначения, не рекомендую, просто выброшенные деньги. Особенности. • Количество сенсоров – один, режим переключения ( touch-on/touch-off ), а также программируемая …

Одноканальный емкостной сенсор – AT42QT1012Views: 2496 Описание сенсора [wpdm_file id=242] Незаконченный проект, так-как сенсор не оправдал своего назначения, не рекомендую, просто выброшенные деньги. Особенности. • Количество сенсоров – один, режим переключения ( touch-on/touch-off ), а также программируемая …