Views: 612

REFERENCE CLOCK

OUTPUT MODULE

Модуль формирования опорного тактового сигнала

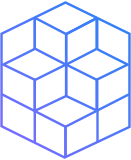

Модуль опорного тактового сигнала обеспечивает возможность посылать сигнал синхронизации на тактовый опорный выходной контакт или контакты (CLKR) в зависимости от конфигурации выводов микроконтроллера. Выход опорного тактового также может быть использован в качестве сигнала для других периферийных устройств, таких как модулятор сигнала данных (DSM), сканер памяти и модуль таймера.

Модуль опорного тактового имеет следующие особенности:

• Выбор источника синхронизации с использованием регистра CLKRCLK

• Программируемый делитель частоты сигнала

• Выбираемый рабочий цикл сигнала

БЛОК СХЕМА МОДУЛЯ

ФОРМИРОВАНИЕ ФОРМЫ СИГНАЛА

Базовым свойством модуля это выбрать источник сигнала, разделить его на требуемое значение и возможность сформировать базовую форму со стандартной длительностью 25-50-75%.

Источник синхронизации

Вход для выходного тактового сигнала можно выбрать с помощью регистра CLKRCLK.

Синхронизация опорного сигнала

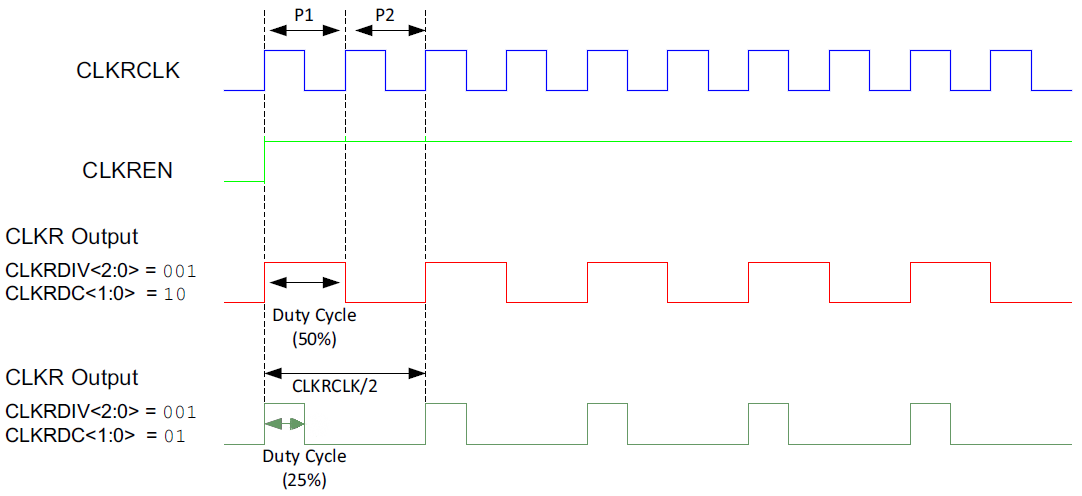

После включения модуля опорного тактового сигнала, установлен (CLKREN), модуль обеспечивается запуск формирования тактового сигнала без помех, при пуске. Когда отключается, выходной сигнал будет отключен немедленно.

Делители частоты и тактовые генераторы могут быть изменены при

включенном модуле, но на выходе могут возникать сбои формы сигнала. Чтобы избежать возможных сбоев, делители тактовых импульсов и тактовые циклы должны быть изменены только тогда, когда CLKREN очищен (модуль отключен).

Программируемый делитель частоты

Выбранный входной тактовый сигнал модуль может разделить в диапазоне от 2 до 128. Частота деления выбирается установкой значения битов DIV <2: 0> регистре CLKRCON.

Доступны следующие конфигурации:

• Base FOSC value

• FOSC divided by 2

• FOSC divided by 4

• FOSC divided by 8

• FOSC divided by 16

• FOSC divided by 32

• FOSC divided by 64

• FOSC divided by 128

Значения делителя частоты может быть изменена во время работы модуля, однако, чтобы предотвратить сбои на выходе формирователя, бит DIV <2: 0> должен быть изменен только при отключенном модуле (EN = 0).

Выбор рабочего цикла

Биты DC <1:0> регистра CLKRCON могут использоваться для изменения рабочего цикла выходного сигнала. Для всех тактовых частот можно выбрать рабочий цикл 25%, 50% или 75%, за исключением значения FOSC без делителя!

Рабочий цикл может быть изменен, когда модуль включен; однако, чтобы предотвратить сбои на выходе, биты DC <1:0> должны быть изменены только тогда, когда модуль отключен (EN = 0).

Примечание

Бит DC1 сбрасывается на «1». Это делает рабочий цикл по умолчанию 50%, а не 0%.

Работа в режиме сна

Тактовый сигнал на выходе модуля связан с системным тактовым генератором. Когда устройство переходит в режим сна, выходы модуля останутся в их текущем состоянии. Это будет иметь непосредственное влияние на периферийные устройства если они используют выходной сигнал этого модуля в качестве входного сигнала. В настройках модуля не должно происходить никаких изменений при входе или выходе из режима сна.

Регистры управления модулем

CLKRCON

| R/W-0/0 | U-0 | U-0 | R/W-1/1 | R/W-0/0 | R/W-0/0 | R/W-0/0 | R/W-0/0 |

| EN

|

DC<1:0>

|

DIV<2:0>

|

|||||

| bit 7 | bit 6 | bit 5 | bit 4 | bit 3 | bit 2 | bit 1 | bit 0 |

| bit 7

|

EN: Бит включения модуля 1 = Модуль включен 0 = Модуль выключен |

| bit 6-5 | не используются при чтении значение 0 |

| bit 4-3

|

DC<1:0>: Биты выбора рабочего цикла (1) 11 = рабочий цикл выходов часов 75% 10 = Рабочий цикл выходов часов составляет 50% 01 = Рабочий цикл выходов часов составляет 25% 00 = рабочий такт выходов 0% |

| bit 2-0

|

DIV<2:0>: Биты делителя частоты 111 = Базовое значение часов, деленное на 128 110 =Базовое значение частоты, деленное на 64 101 = Базовое значение частоты, деленное на 32 100 = Базовое значение частоты, деленное на 16 011 = Базовое значение частоты, деленное на 8 010 = базовое значение частоты, деленное на 4 001 = Базовое значение частоты, деленное на 2 000 = Базовое значение частоты |

Примечание

Биты действительны для значений делителя тактовых импульсов от двух или более, базовая частота не может сформирована по длительности рабочего цикла.

CLKRCLK

| U-0 | U-0 | U-0 | U-0 | U-0 | R/W-0/0 | R/W-0/0 | R/W-0/0 |

| CLK<2:0>

|

|||||||

| bit 7 | bit 6 | bit 5 | bit 4 | bit 3 | bit 2 | bit 1 | bit 0 |

| bit 7-3 | не используются при чтении значение 0 |

| bit 2-0

|

CLK<2:0>: биты выбора источника CLKR 111 = не реализованы 110 = не реализованы 101 = не реализованы 100 = SOSC 011 = MFINTOSC (500 kHz) 010 = LFINTOSC (31 kHz) 001 = HFINTOSC 000 = FOSC |

Регистры связанные с этим модулем

| CLKRCON | Включение модуля настройка делителя и рабочего цикла. |

| CLKRCLK | Выбор источника тактовой частоты. |

| PMD0 | Регистр отключения периферийных модулей, он предназначен для значительного снижения энергопотребления, особенно в режиме сна. |

| RxyPPS | Регистры подключения входов выходов периферийных модулей. |

Тестирование модуля

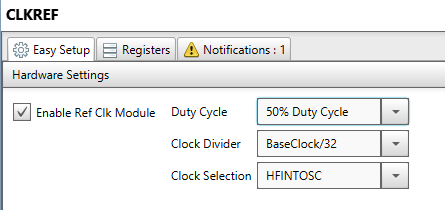

Конфигурация

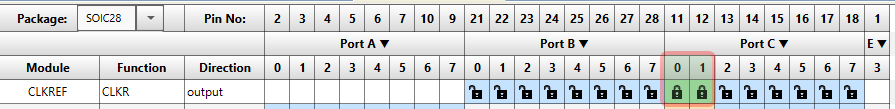

Настройка выхода модуля. Выход может быть подключен к любому выходу потов B и C, что интересно можно подключить не к одному порту, а к нескольким или ко всем!!!

Вариант настройки выхода на два вывода порта C.

Модуль позволяет вывести на выход при подключении от HFINTOSC (64МГц задана) только при значении битов DIV<2:0> = 010 делитель на 4, т.е с значения 16 Мгц., при попытки настроить на более высокие частоты работать не будет. Т.е. мы не можем фторировать частоты выше чем опорная частота деленная на 4.

Рабочий цикл работает правильно, если выберем длительность 0% частота на выходе модуля отсутствует.

Зададим следующие параметры

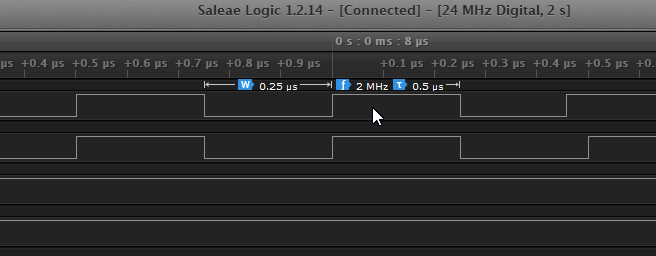

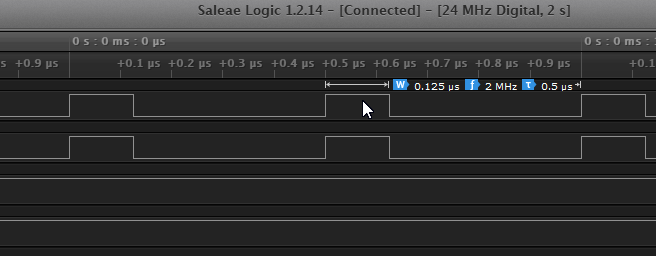

Проверим форму сигнала при настройке на разные длительности, на выходе мы получим частоту 2 мГц.

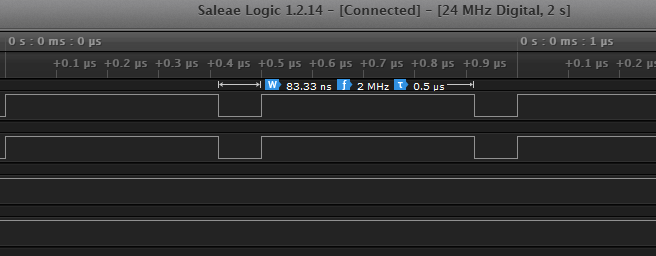

Частота 2 Мгц, длительность 50%

Настроен выход на одновременно на две ноги микроконтроллера порты PORTC0 и PORTC1

Частота 2 Мгц, длительность 25%

Настроен выход на одновременно на две ноги микроконтроллера порты PORTC0 и PORTC1

Частота 2 Мгц, длительность 75%

Настроен выход на одновременно на две ноги микроконтроллера порты PORTC0 и PORTC1

Стать по теме

Тестирование модуля генератора

Analog-to-Digital Converter with Computation Technical Brief

- Продолжение следует….

Это может быть интересно

Flight controller for FPV drone.Views: 79 Reverse engineering of a flight controller (SpeedyBee F405 V4 55A 30×30 Stack). Мене зацікавила конструкція основних компонентів FPV-дрона. Першим варіантом, який я розглянув, був контролер польоту від китайської …

Flight controller for FPV drone.Views: 79 Reverse engineering of a flight controller (SpeedyBee F405 V4 55A 30×30 Stack). Мене зацікавила конструкція основних компонентів FPV-дрона. Першим варіантом, який я розглянув, був контролер польоту від китайської … Altium Designer my Libraries, Project templates, System settings by Catcatcat V24.0 PROViews: 556 Назвемо цей варіант поновлення для професіоналів і не тільки. Що нового? 1. Повністю змінено структуру параметрів бази даних компонента. Це дозволило повноцінної роботи Актив ВОМ. Ви відразу отримуєте …

Altium Designer my Libraries, Project templates, System settings by Catcatcat V24.0 PROViews: 556 Назвемо цей варіант поновлення для професіоналів і не тільки. Що нового? 1. Повністю змінено структуру параметрів бази даних компонента. Це дозволило повноцінної роботи Актив ВОМ. Ви відразу отримуєте … MPLAB® Code ConfiguratorViews: 1825 MPLAB ® Code конфигуратор (MCC) является свободно распространяемым плагином, это графическая среда программирования, которая генерирует бесшовный, легкий для понимания кода на Cи, чтобы вставить его в свой проект.

MPLAB® Code ConfiguratorViews: 1825 MPLAB ® Code конфигуратор (MCC) является свободно распространяемым плагином, это графическая среда программирования, которая генерирует бесшовный, легкий для понимания кода на Cи, чтобы вставить его в свой проект. MCC PIC24 – модуль OUTPUT COMPARE – режиме ШИМViews: 1312 Во многих системах управления, для формирования управляющих сигналов требуется модуль ШИМ, он позволяет не только формировать импульсы заданной длительности, но и с применением обычного RC фильтра строить простые …

MCC PIC24 – модуль OUTPUT COMPARE – режиме ШИМViews: 1312 Во многих системах управления, для формирования управляющих сигналов требуется модуль ШИМ, он позволяет не только формировать импульсы заданной длительности, но и с применением обычного RC фильтра строить простые … Проект с использованием MCC часть 14Views: 1122 С выводом данных на дисплей мы справились (но могу сразу сказать библиотеку графики к этой статьи пришлось доработать, поэтому в этом проекте она обновлена). У нас на текущем …

Проект с использованием MCC часть 14Views: 1122 С выводом данных на дисплей мы справились (но могу сразу сказать библиотеку графики к этой статьи пришлось доработать, поэтому в этом проекте она обновлена). У нас на текущем … Проект с использованием MCC часть 05Views: 2255 Эту часть назовем так как избавься от delay, там где а это реально не надо. Для это нам потребуется научиться использовать прерывания и работать с таймерами. Что такое …

Проект с использованием MCC часть 05Views: 2255 Эту часть назовем так как избавься от delay, там где а это реально не надо. Для это нам потребуется научиться использовать прерывания и работать с таймерами. Что такое … 12-BIT A/D CONVERTER WITH THRESHOLD DETECT на примере PIC24FJ128GA204Views: 967 Введение. 12-битный модуль A/D Converter является усовершенствованной версией 10-битного модуля, предлагаемого на некоторых устройствах PIC24. Оба модуля являются преобразователями, в своих ядрах, с последовательным приближением (SAR), в окружении …

12-BIT A/D CONVERTER WITH THRESHOLD DETECT на примере PIC24FJ128GA204Views: 967 Введение. 12-битный модуль A/D Converter является усовершенствованной версией 10-битного модуля, предлагаемого на некоторых устройствах PIC24. Оба модуля являются преобразователями, в своих ядрах, с последовательным приближением (SAR), в окружении … Сумеречное релеViews: 1693 Реле управления освещением, датчик день-ночь – одним словом фотореле для управления освещением или формирования сигнала для системы умный дом о понижении или повышении освещенности относительно заданного уровня. Реле выполнено по классической схеме, конденсаторный блок питания, от сети переменного тока …

Сумеречное релеViews: 1693 Реле управления освещением, датчик день-ночь – одним словом фотореле для управления освещением или формирования сигнала для системы умный дом о понижении или повышении освещенности относительно заданного уровня. Реле выполнено по классической схеме, конденсаторный блок питания, от сети переменного тока … Altium Designer my setup system and project structureViews: 1094 Используйте только последнее обновление!!! Updates https://catcatcat.d-lan.dp.ua/altium-designer-my-libraries-project-templates-system-settings-by-catcatcat-v23-09/ Тут хочу поделиться как я настраиваю Altium Designer и как я использую файлы DXPPreferences.DXPPrf для быстрой конфигурации и получения …

Altium Designer my setup system and project structureViews: 1094 Используйте только последнее обновление!!! Updates https://catcatcat.d-lan.dp.ua/altium-designer-my-libraries-project-templates-system-settings-by-catcatcat-v23-09/ Тут хочу поделиться как я настраиваю Altium Designer и как я использую файлы DXPPreferences.DXPPrf для быстрой конфигурации и получения … Просто о структурах и объединениях в СиViews: 2396 Какие задачи нам позволяют решать структуры и объединения? Для разработчика встроенных систем эффективность и компактность кода всегда на первом месте. Если программировании на Ассемблере ты сам определяешь как …

Просто о структурах и объединениях в СиViews: 2396 Какие задачи нам позволяют решать структуры и объединения? Для разработчика встроенных систем эффективность и компактность кода всегда на первом месте. Если программировании на Ассемблере ты сам определяешь как …