Views: 4088

Контроллер DMA – Прямой доступ к памяти.

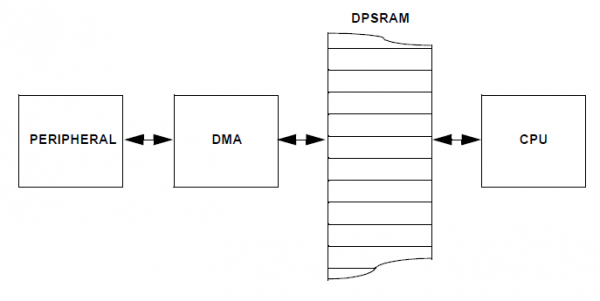

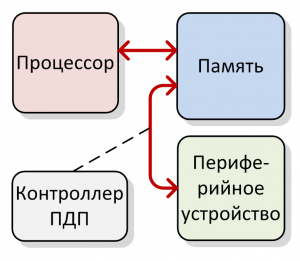

Для быстрого сбора или передачи данных в автоматическом режиме, что бы не отнимать ресурсы процессора на выполнения основной задачи, предназначен Контроллер DMA. Он позволяет организовывать каналы автоматического сбора и отправки данных на периферийные устройства. Контроллер DMA – присутствует в контроллера PIC24H, позволяет организовать обмен данными с устройствами посредством двух портовой памяти DPSRAM.

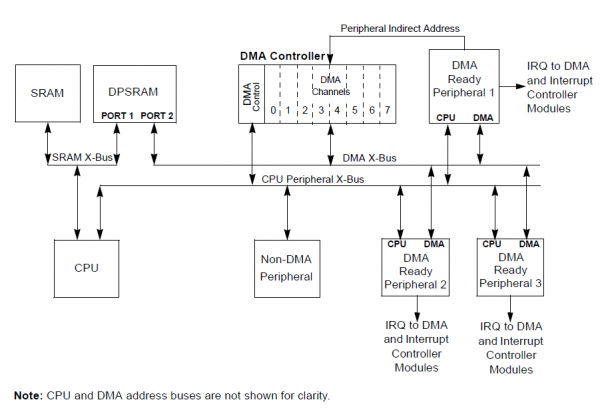

Контроллер DMA передает данные между регистрами периферийных устройств и данными в пространства SRAM. Подсистема DMA PIC24H использует двух портовые функции памяти SRAM (DPSRAM) и регистры структуры, которые позволяют работать DMA через ее собственные, независимые адреса и шины данных без влияния на работу процессора. Эта архитектура устраняет необходимость в цикле задержки, который останавливает CPU, когда более высокий приоритет DMA запрашивает передачу данных. Оба процессор и контроллера DMA может писать и читать в/из адресов в пространстве данных без помех, в режиме реального времени. Кроме того, операции DMA и передачи данных в/из памяти и периферийных устройств не влияет на обработку данных процессором. Например, когда во время выполнения самостоятельного программирования (RTSP), процессор не выполняет никаких инструкций, пока RTSP не закончена. Это условие, однако, не влияет на передачу данных в/из памяти для периферийных устройств.

Контроллер DMA поддерживает восемь независимых каналов. Каждый канал может быть настроен на обмен данными для выбранного периферийного устройства. Периферийные устройства, поддерживаемых контроллером DMA включают:

- ECAN™ technology

- 10-bit/12-bit Analog-to-Digital Converter (ADC)

- Serial Peripheral Interface (SPI)

- UART

- Input Capture

- Output Compare

Кроме того, выполнение обмена данными контроллером DMA могут быть вызваны таймерами, а также внешними прерываниями. Каждый канал DMA является однонаправленным. Два DMA канала могут быть настроены на направления на чтение и запись в периферийное устройство. Если более чем один канал получает запрос на передачу данных, то простая схема фиксированных приоритетов, основанная на номере канала, определяет какой канал завершает передачу и какой канал или каналы, остаются в ожидании. Каждый DMA канал может перемещать блок до 1024 элементов данных, после чего он генерирует прерывание для процессора, чтобы указать, что блок готов для обработки данных.

DMA контроллер обеспечивает следующие функциональные возможности:

- Восемь каналов DMA

- Режим косвенной адресации с пост-приращение

- Режим косвенной адресации без пост-приращение

- Периферийные косвенным режимом адресации (периферический генерирует адрес назначения)

- Прерывание для CPU после заполнения или передачи половины или полного буфера данных

- Передача байта или слова данных

- Фиксированные уровни приоритета каналов DMA

- Руководство (программное обеспечение) или автоматической (периферический запросы DMA) начала передачи

- Одиночный или автоматический режим повтора передачи блока данных

- Пинг-понг режиме (автоматическое переключение между двумя адресами DPSRAM начала после каждого полного блока передачи )

- DMA запрос для каждого канала может быть выбран из любого поддерживаемого источника прерывания

- Поддержка отладки функций

DMA регистры.

Каждый канал DMA имеет набор из шести регистров состояния и управления.

DMAxCON: Регистр управления каналом

Этот регистр предназначен для включения/отключения канала, задание передаваемого размера данных (слово/байт), направления передачи данных, метод прерывания, выбор режим адресации, режим записи данных обычный или режим работы Null.

DMAxREQ: Регистр настройки соответствия канала DMA периферийному устройству через IRQ

Этот регистр связывает канал DMA с конкретным периферийным устройством, путем загрузки в регистр номера DMA периферийного устройства. Через этот регистр канал DMA получает запрос выполнить передачу данных, когда периферийное устройство подготовит данные и выставит прерывание.

DMAxSTA: Стартовый адрес для буфера А в DPSRAM памяти

Этот регистр указывает начальный адрес смещения для буфера А от базового адреса DPSRAM блока данных для передачи по каналу DMA_Х в или из DPSRAM. Чтение этого регистра возвращает значение адрес смещения DPSRAM после последней передачи . Запись в этот регистр то время как соответствующий канал DMA включен (т.е. активный) может привести к непредсказуемому поведению и этого следует избегать.

DMAxSTB: Стартовый адрес для буфера В в DPSRAM памяти

Этот регистр указывает начальный адрес смещения для буфера В от базового адреса DPSRAM блока данных для передачи по каналу DMA_Х в или из DPSRAM. Чтение этого регистра возвращает значение адрес смещения DPSRAM после последней передачи. Запись в этот регистр то время как соответствующий канал DMA включен (т.е. активный) может привести к непредсказуемому поведению и этого следует избегать.

DMAxPAD: Адрес регистра данных периферийного устройства

Этот регистр чтения/записи содержит указатель на регистра данных периферийного устройства. Запись в этот регистр то время как соответствующий канал DMA включен (т.е. активный) может привести к непредсказуемому поведению и этого следует избегать.

DMAxCNT: Регистр количества данных, загружаемых в буфер

Этот регистр содержит размер буфера данных. DMAxCNT + 1 представляет количество запросов которые должен обслужить DMA канал для передачи блока данных. То есть, если значение записанное в регистр DMAxCNT = ‘0’, будет передаваться один элемент. Значение регистра DMAxCNT не зависит от размера данных передачи (размер бита в DMAxCON регистра). Запись в этот регистр то время как соответствующий канал DMA включен (т.е. активный) может привести к непредсказуемому поведению и этого следует избегать.

В дополнение к отдельному каналу DMA регистров контроллера DMA имеет три регистров DMA статуса.

DSADR: Регистр адреса последнего обращения в память DPSRAM

Этот 16-разрядный, с доступном только для чтения, регистр состояния, является общим для всех каналов DMA. Она захватывает адрес по которому было последнее обращение к памяти DPSRAM (чтение или запись). Он сбрасывается при сбросе и, следовательно, содержит значение ‘0x0000 ‘, если его прочитать до начала любой активности DMA. Этот регистр доступный в любое время, но в первую очередь предназначена как для отладочных функций.

DMACS0: Регистр 0 состояния контроллера DMA

Этот 16-разрядный, с доступном только для чтения, регистр состояния, содержит флаги ошибок записи в данных в периферийное устройство и в DPSRAM память.

DMACS1: Регистр 1 состояния контроллера DMA

Этот 16-разрядный, с доступном только для чтения, регистр состояния, содержит указание какой канал DMA совсем недавно был активным и показывает какой канал работает в режиме Пинг-понг.

DMA контроллер – блок схема

Пример использование контроллера DMA для получение данных от АЦП, помещение его в массив для последующей обработки процессором.

Задача следующая, необходимо настроить работу АЦП в непрерывном режиме измерений, а работу DMA контроллера для сбора 128 байт данных и формирования прерывания для процесса обработки данных.

Настройка АЦП (пример для контроллера PIC24HJ256GP206)

void initADC (void)

{

/*настройка АЦП для режима автоматических измерений*/

/*настройка аналоговых входов для АЦП1*/

AD1PCFGH=0b1111111111111111;// 0-аналоговый вход 1 - цифровой

AD1PCFGL=0b1111111011111110;

// +-------+------ PCFG8: вход AN0 - опорное, AN8 - вход измерения (AN9 контроль напряжения батарейки)

/*выбор основного и альтернативного аналогового входа*/

/*альтернативный вариант может использоваться для выбора контроля источника вторичного напряжения*/

AD1CHS0 = 0b00000000001000; // AN0 подключить к CH8, настройки альтернативного выбора не используются

/*сканирование по входам не используется*/

AD1CSSL = 0;

AD1CSSH = 0;

/*рамер буфера*/

AD1CON4=0b0000000000000111;

// +++------- DMABL<2:0>:111 = выделить буфер для измерений 128 слов.

// 1111100000010

AD1CON3=0b0001110000111111;

// | |||||++++++++------- ADCS<7:0>: 63 задание длительности TAD

// | +++++--------------- SAMC<4:0>: TAD=28 задание времени выборки в TAD

// +---------------------- ADRC: 0-синхронизация от системного генератора

/*выбор источника опорного напряжения*/

AD1CON2=0b0010000000111110;

// ||| ||| |||||+------- ALTS:всегда использует один канал для измерения (MUX A)

// ||| ||| ||||+-------- BUFM:Начинается заполнение первой половины буфера на прерывание первой и второй половины буфера на следующее прерывание

// ||| ||| ++++--------- SMPI<3:0>: Увеличивает адресов DMA или генерирует прерывание после завершения 16 измерений

// ||| |++--------------- CHPS<1:0>:только канал CH0

// ||| +----------------- CSCNA:сканирование отключено

// +++-------------------- VCFG<2:0>:VREF+ - External VREF; VREF- - AVSS

/*включить преобразование, в режиме автоматического, постоянного преобразования*/

AD1CON1=0b1000010011100100;

// | || |||||| ||

// | || |||||| |+-------- ASAM: 1 = Отбор проб начинается сразу после последнего преобразования.

// | || |||||| +--------- SIMSAM:0

// | || ||||||

// | || |||+++----------- SSRC<2:0>: подразумевается внутренний счетчик окончания выборки и начала преобразования

// | || |++-------------- FORM<1:0>:00 = Целое (DOUT = 0000 dddd dddd dddd)

// | || +---------------- AD12B: 12-bit, 1-channel ADC operation

// | |+------------------

// | +-------------------- ADSIDL: 0 = Продолжить работу модуля в Idle режиме

// +---------------------- ADON: ADC Модуль работает

}